### A Resilience Roadmap

Sani Nassif, Juan-Antonio Carballo, Andrew Kahng, Larry Wissel, Kevin Cao, Nikil Mehta, Chris Wilkerson

1

### **Motivation**

- Document current trends in various resilience components to better motivate R&D priorities.

In the context of this CCC study.

- Identify problems, potential solutions, future gaps.

- Guided by ITRS methodology.

- Focus on technology, devices and base circuits.

- ♦ Target: ITRS Design Chapter.

- Timeframe: next ITRS update (late '09).

- Make results and methodology reproducible.

- Open source the scripts and models.

# Team and Proposed Roles

- Juan-Antonio Carballo (IBM), Andrew Kahng (UCSD).

- ITRS coordination.

- Larry Wissel (IBM).

- Provide extrinsic noise models.

- Kevin Cao (ASU).

- Provide technology models.

- Nikil Mehta (Caltech).

- Run simulations.

- Chris Wilkerson (Intel).

- Sanity checks.

- Sani Nassif (IBM).

- Overall coordination, provide intrinsic noise models.

#### **Current Results**

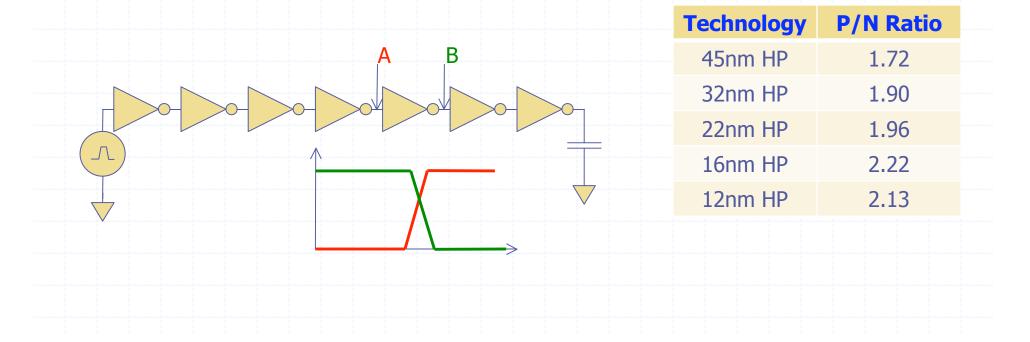

## Basics: P to N Ratio

- Soal: find correct P to N ratio so that rise and fall times are approximately equal.

- Used in other scripts to determine ratios.

- Methodology: create a string of 7 inverters, measure rise/fall times in the middle, adjust ratio to make them equal.

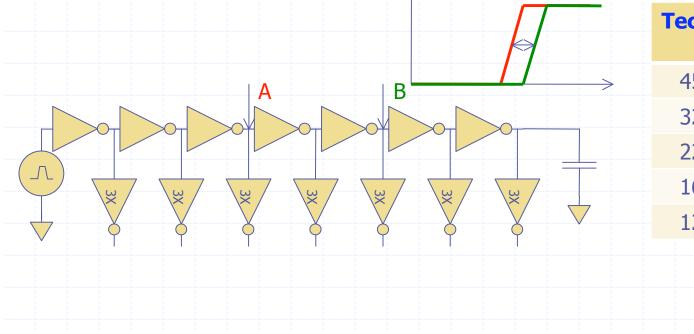

## **Basics: Pair Delay**

♦ Goal: find pair delay of FO4 chain of inverters.

- Used to set various pulse widths, rise/fall times etc...

- Methodology: create a string of 7 FO4 inverters, measure delay of 2 inverters.

| Technology | Pair delay<br>(ps) |  |

|------------|--------------------|--|

| 45nm HP    | 22.63              |  |

| 32nm HP    | 19.59              |  |

| 22nm HP    | 17.76              |  |

| 16nm HP    | 16.07              |  |

| 12nm HP    | 15.86              |  |

|            |                    |  |

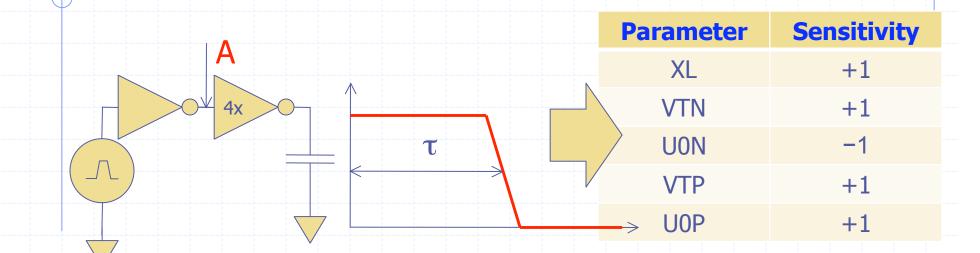

#### Inverter

- ♦ Goal: find failure point for inverter.

- ♦ Failure = no pulse propagation.

- Metric: fall time in a string of inverters.

#### Methodology:

- 1. Find sensitivity of metric to variations in  $\Delta L$ ,  $V_{THN}$ ,  $V_{THP}$ ,  $U_{0N}$ ,  $U_{0P}$ . (by perturbing each parameter and monitoring the sign of the change in the metric).

- 2. Move parameters in direction to make metric worse.

- 3. Use bisection to find point at which failure occurs.

#### Methodology in Pictures

Sensitivity is independent of any distributional assumptions on parameters (i.e. μ and σ).

Failure σ does depend on distributions, so script expects user to specify the σ's.

#### **Inverter Results**

| Technology | Sigma L<br>(nm) | Sigma VT<br>(mV) | Sigma U<br>(as % of μ) | Failure<br>Sigma |

|------------|-----------------|------------------|------------------------|------------------|

| 45nm HP    | 3.0             | 23               | 3                      | Х                |

| 32nm HP    | 2.0             | 33               | 3                      | Х                |

| 22nm HP    | 1.5             | 48               | 3                      | Х                |

| 16nm HP    | 1.0             | 66               | 3                      | 11.4             |

| 12nm HP    | 0.8             | 88               | 3                      | 8.26             |

- X means sigma too large to estimate accurately. (probability is basically zero).

- Results are consistent with previously observed trends.

- Adjusting the Sigma values has the expected impact on the failure Sigma.

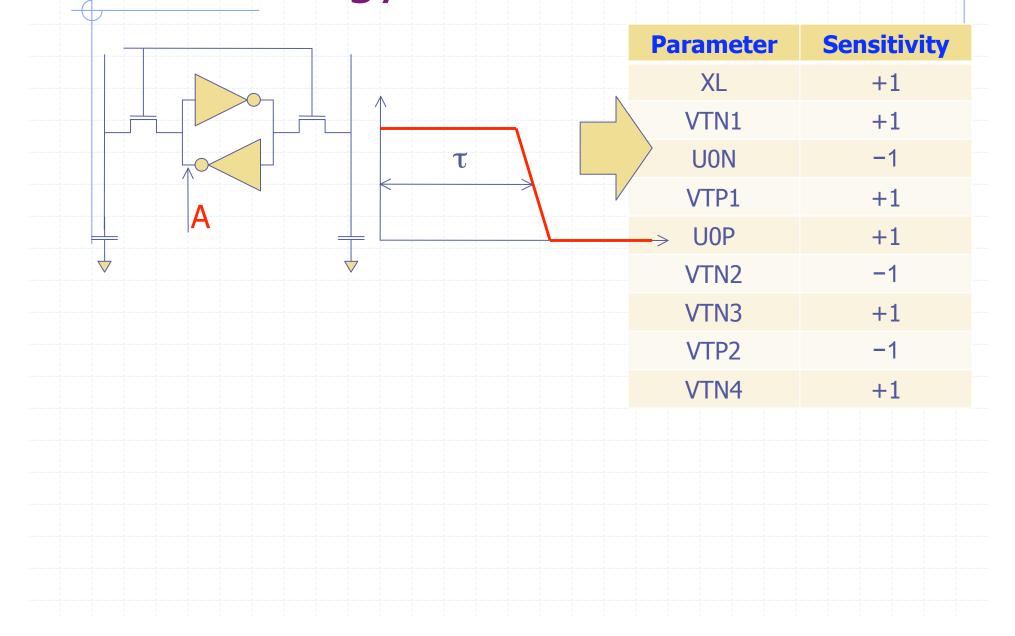

# SRAM

- ♦ Goal: find failure point for an SRAM cell.

- ♦ Failure = unable to write to cell.

- Metric: delay to internal node changing value.

#### Methodology:

- **1.** Find sensitivity of metric to variations in  $\Delta L$ , the V<sub>TH</sub> of each device, U<sub>0N</sub>, U<sub>0P</sub>. (by perturbing each parameter and monitoring the sign of the change in the metric).

- 2. Move parameters in direction to make metric worse.

- 3. Use bisection to find point at which failure occurs.

## Methodology in Pictures

#### **SRAM Results**

| Technology | Sigma L<br>(nm) | Sigma VT<br>(mV) | Sigma U<br>(as % of μ) | Failure<br>Sigma |

|------------|-----------------|------------------|------------------------|------------------|

| 45nm HP    | 1.0             | 47               | 3                      | 6.64             |

| 32nm HP    | 0.6             | 66               | 3                      | 5.47             |

| 22nm HP    | 0.4             | 96               | 3                      | 4.57             |

| 16nm HP    | 0.3             | 133              | 3                      | 3.93             |

| 12nm HP    | 0.2             | 177              | 3                      | 3.68             |

|            |                 |                  |                        |                  |

Sigma L reduced (because of SRAM regularity)

Sigma VT increased (because of device size)

### Status

- First version completed and reviewed.

- Lots of potential remains for a more detailed study.

- ITRS design chapter was amended with a resilience section.

- Currently in the DFM section.

- Will separate as more material is generated.

Prof. Cao will host the scripts, documents, and models as part of the PTM web site.

Release target date yet to be set.