R

ABILITY

André DeHon, Nick Carter and Heather Quinn, Editors

March 3, 2011

**Contributors:** Sarita Adve, Marcos Aguilera, Carl Anderson, Paul Armijo, Todd Austin, Sankar Basu, Lori Bechtold, Shawn Blanton, Shekhar Borkar, Younes Boulghassoul, Keith Bowman, Greg Bronevetsky, James Browne, Nicholas Carter, Vikas Chandra, Tim Cheng, Pierre Chor-Fung Chia, Lewis Cohn, John Daly, Chitaranjan Das, J.L. de Jong, Nathan DeBardeleben, Erik deBenedictis, André DeHon, Eliezer Dekel, Bill Eklow, Glenn A Forman, Armando Fox, Tim Gallagher, Donald S. Gardner, Kinshuk Govil, John Gustafson, Eric Hannah, William Harrod, William Heidergott, John Hiller, Andrew Huang, Ravi Iyer, David Kaeli, Zbigniew Kalbarczyk, Kevin Kemp, Prabhakar Kudva, Kimmo Kuusilinna, Shih-Lien Lu, James Lyke, William M. Jones Jr, Nikil Mehta, Sarah Michalak, Subhasish Mitra, Claude Moughanni, Shubu Mukherjee, Helia Naeimi, Sani Nassif, Suriyaprakash Natarajan, Eugene Normand, Kevin Nowka, Ishwar Parulkar, Karthik Pattabiraman, Mark Porter, Heather Quinn, Charles Recchia, Anthony Reipold, Pia Sanda, Sumeet Sandhu, John Savage, Bianca Schroeder, Sanjit Seshia, Allan Silburt, James Smith, Rafi Some, Daniel Sorin, Jon Stearley, Gary Swift, David Tennenhouse, Chandra Tirumurti, Steve Trimberger, Ian Troxel, David Walker, Shi-Jie Wen, Chris Wilkerson, Alan Wood, Vivian Zhu

# Disclaimer

The material in this document reflects the collective views, ideas, opinions and findings of the study participants only, and not those of any of the universities, corporations, or other institutions with which they are affiliated. Furthermore, the material in this document does not reflect the official views, ideas, opinions and/or findings of National Science Foundation, the Computing Research Association, or of the United States government.

# **Organization and Contributions**

## **Organizers:**

- Nicholas P. Carter, Intel Corporation

- André DeHon, University of Pennsylvania

- Heather M. Quinn, Los Alamos National Laboratory

## **Core Working Group:**

- Sarita V. Adve, University of Illinois Urbana-Champaign

- Todd Austin, University of Michigan

- Andrew "Bunnie" Huang, Chumby Industries, Inc.

- Ravishankar K. Iyer, University of Illinois Urbana-Champaign

- Subhasish Mitra, Stanford University

- Sani Nassif, IBM

- John Savage, Brown

- David Walker, Princeton University

- Gary Swift, Xilinx Corporation

## **Focus Group Leaders:**

- Commercial and Consume Electronics Todd Austin, University of Michigan

- Infrastructure Zbigniew Kalbarczyk, University of Illinois Urbana-Champaign

- Life Critical Mark Porter, Medtronics

- Aerospace Heather M. Quinn, Los Alamos National Laboratory

- Large-Scale Systems

- Greg Bronevetsky, Lawerence Livermore National Laboratory

- Armando Fox, University of California at Berkeley

- Sarah Michalak, Los Alamos National Laboratory

- Roadmap Sani Nassif, IBM

- Metrics

- Subhasish Mitra, Stanford University

- Pia Sanda, IBM

## Wiki Maintenance:

• Nikil Mehta, California Institute of Technology

## **CCC Liasons:**

- David Kaeli, Northeastern University

- David Tennenhouse, New Venture Partners

## **Participants:** For full list see Page 81.

# Forward

This document reflects the thoughts of a group of researchers from universities, industry, and research laboratories on potential avenues of research to change how reliability is addressed in the world-wide computing infrastructure. The report itself is the direct result of meetings with these researchers during 2009. This study and the material assembled is based upon work supported by the National Science Foundation under Grant 0637190 to the Computing Research Association for the Computing Community Consortium.

The goal of the study was to define a new vision for the future of reliable system design, and not to propose a potential reliability method. Further, the report itself was assembled in just a few months in 2010 from input by the participants. As such, all inconsistencies reflect either areas where there really are significant open research questions, or misunderstandings by the editors. There was, however, complete agreement about the key challenges that surfaced from the study, and the potential value that sharing reliability tasks across the entire computing stack might advance the field of reliable computing.

We are grateful to work with so many dedicated people that put in many long hours to help the study along. David Kaeli and David Tennenhouse helped sheppard us through the CCC process. Todd Austin, Zbigninew Kalbarczyk, Mark Porter, Greg Bronevetsky, Armando Fox, Sarah Michalak, Subhasish Mitra, Sani Nassif, and Pia Sanda helped lead the focus groups which helped us gain an understanding of where particular research communities were, updating the ITRS roadmap, and researching what metrics were needed. Nikil Mehta helped keep the wiki updated and running. We are grateful for all of your help.

We are honored to have been part of this study, and wish to thank the study members for their time, their effort, and their insight.

André DeHon, Nick Carter, and Heather Quinn

# Contents

| 1 Executive Summary                                                          | 1  |

|------------------------------------------------------------------------------|----|

| 2 Vision                                                                     | 6  |

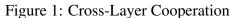

| 2.1 Goal                                                                     | 7  |

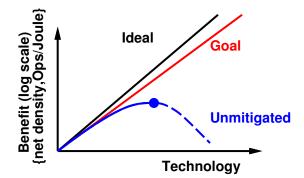

| 2.2 Trends                                                                   | 8  |

| 2.3 Why Now?                                                                 | 14 |

| 2.4 How is it done today?                                                    | 15 |

| 2.5 What is New?—Keys to the Solution                                        |    |

| 2.6 What Can We Accomplish?                                                  |    |

| 2.7 Why Do This?                                                             |    |

| 2.8 Why Government Leadership?                                               |    |

| 2.9 Summary                                                                  |    |

| 3 Examples and Illustrative Scenarios                                        | 25 |

| 3.1 Resilience Tasks                                                         |    |

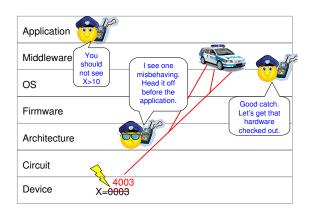

| 3.2 Cross-Layer Reliable Computing Systems                                   |    |

| 3.2.1 Detection                                                              |    |

| 3.2.2 Diagnosis                                                              |    |

| 3.2.3 Reconfiguration                                                        |    |

| 3.2.4 Recovery                                                               |    |

| 3.2.5 Adaptation                                                             |    |

| 3.3 Cross-Layer Reliable Systems-on-Chip                                     |    |

| 3.4 Early Support for Reliable and Adaptable Application Software, Operating |    |

| tems, and Middleware                                                         | •  |

| 4 Challenge Problems and Areas of Pain                                       | 33 |

| 4.1 Challenge Problems by Constituency Group                                 |    |

| 4.1 Consumer Electronics (CE)                                                |    |

| 4.1.2 Aerospace (AS)                                                         |    |

| 4.1.3 Large-Scale Systems (LS)                                               |    |

| 4.1.4 Life-Critical Systems (LC)                                             |    |

| 4.1.5 Infrastructure (IS)                                                    |    |

| 4.2 Challenge Roundup                                                        |    |

| 4.2.1 Late-Bound Information                                                 |    |

| 4.2.2 Instantaneous Operational Information                                  |    |

| 4.2.3 Information about Application Requirements                             |    |

| 4.2.4 Information about Health of Components                                 |    |

| 4.2.5 Information about Treatmost Components from Heterogeneous S            |    |

| 4.2.6 Granularity of Information Exploitation—Adaptation and Repair .        |    |

| 4.2.7 Incomplete Information on Component and System Reliability Weak        |    |

| 4.2.8 Analog and Passive Elements                                            |    |

| 5             | Scie                                                                                                                                                        | nce Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>40</b>                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|               | 5.1                                                                                                                                                         | Repair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                                                                  |

|               |                                                                                                                                                             | 5.1.1 Granularity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                                  |

|               |                                                                                                                                                             | 5.1.2 Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                  |

|               | 5.2                                                                                                                                                         | Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                                                                  |

|               | 5.3                                                                                                                                                         | Multi-layer Interfaces and Cooperation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                  |

|               | 5.4                                                                                                                                                         | Lightweight Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44                                                                                                                  |

|               | 5.5                                                                                                                                                         | Differential Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                                  |

|               | 5.6                                                                                                                                                         | Scalable Adaptive Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46                                                                                                                  |

|               |                                                                                                                                                             | 5.6.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                                                                  |

|               |                                                                                                                                                             | 5.6.2 Theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                  |

|               | - 7                                                                                                                                                         | 5.6.3 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                                                                  |

|               | 5.7                                                                                                                                                         | Graceful Degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                                                                                                                  |

| 6             | Mis                                                                                                                                                         | sion Impacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                  |

| U             | 6.1                                                                                                                                                         | Saving Lives by Enabling More Powerful and Reliable Life-Critical Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49                                                                                                                  |

|               | 6.2                                                                                                                                                         | Closing the Technology Gap Between Aerospace and Consumer Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                                                                  |

|               | 6.3                                                                                                                                                         | Saving Energy and Improving Service Through Smart Infrastructure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                                  |

|               | 6.4                                                                                                                                                         | Increasing Security on National Mission Computing Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                                                  |

|               | 6.5                                                                                                                                                         | Decreasing Human Liability for In-theater Warfighters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                                                                                  |

| 7             | Edu                                                                                                                                                         | cation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                                  |

|               |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| •             | C4-ma                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| 8             |                                                                                                                                                             | tegic Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                  |

| 8             | 8.1                                                                                                                                                         | Concurrent Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                                                                  |

| 8             |                                                                                                                                                             | Concurrent Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56<br>56                                                                                                            |

| 8             | 8.1                                                                                                                                                         | Concurrent Research       Software and Applications         8.2.1       Concerns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56<br>56<br>56                                                                                                      |

| 8             | 8.1<br>8.2                                                                                                                                                  | Concurrent Research       Software and Applications         8.2.1       Concerns         8.2.2       Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>56<br>56<br>57                                                                                                |

| 8             | <ul><li>8.1</li><li>8.2</li><li>8.3</li></ul>                                                                                                               | Concurrent Research       Software and Applications         8.2.1       Concerns         8.2.2       Impact         Trusted Computing       Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56<br>56<br>56<br>57<br>58                                                                                          |

| 8             | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul>                                                                                                   | Concurrent ResearchSoftware and Applications8.2.1Concerns8.2.2ImpactTrusted ComputingSoftware and Software | 56<br>56<br>57<br>58<br>58                                                                                          |

| 8             | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>                                                                                       | Concurrent ResearchSoftware and Applications8.2.1Concerns8.2.2ImpactTrusted ComputingAnalog ComponentsBackup ComplacencySoftware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56<br>56<br>56<br>57<br>58<br>58<br>58<br>59                                                                        |

| 8             | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Met</li> </ul>                                                                    | Concurrent Research       Software and Applications         Software and Applications       8.2.1         Concerns       8.2.2         Impact       9.2.2         Trusted Computing       9.2.2         Analog Components       9.2.2         Backup Complacency       9.2.2         rics       9.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56<br>56<br>56<br>57<br>58<br>58<br>59<br><b>60</b>                                                                 |